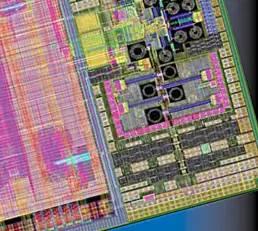

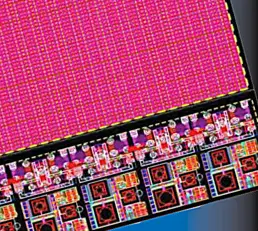

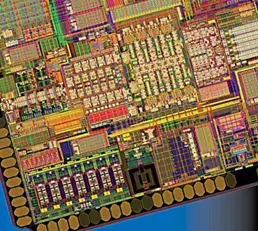

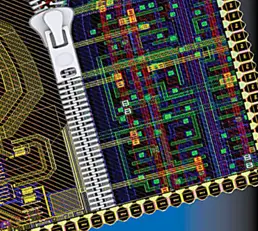

A PORTFOLIO OF ADVANCED SOLUTIONS

Pacific MicroCHIP Corporation (PMCC) is a privately held company providing Application-Specific Integrated Circuit (ASIC) development services and turnkey solutions since 2006. It is headquartered in Los Angeles area, California, USA. PMCC provides niche high-performance ASICs for application in numerous industries. Below are the top 5 industries targeted by our solutions: